Allgemeines

- Projektordner herunterladen und entpacken

- Insgesamt gibt es 29 Punkte

- Die einzelnen Punkte bauen meist nicht aufeinander auf. Statt langer Fehlersuche lieber auf das nächste Beispiel wechseln.

Einschaltverzögerung

Vorbereitung

- Projekt led_delay/led_delay.xise öffnen

Aufgabenstellung

Es ist eine einfache Einschaltverzögerung zu entwerfen. Diese Einschaltverzögerung steuert eine LED an und wird mittels zwei Tasten bedient:

button_toggle- Schaltet das Licht ein bzw. ausbutton_on- Schaltet das Licht in 3 Sekunden ein

Entwurf der Zustandsmaschine

5 Punkte

Zur Realisierung wird eine Zustandsmaschine genutzt.

- Bearbeite die Datei led_delay_fsm.vhd

- Definiere die drei Zuständen

OFF,LIGHTundDELAY - Der Startzustand ist

OFF - Der Eingang

toggle_iwechselt vonLIGHTnachOFFbzw. vonOFFoderDELAYnachLIGHT - Der Eingang

on_iwechselt vonOFFnachDELAY, bei den anderen Zuständen hat er keine Auswirkung - Der Eingang

timeout_ibewirkt ein Wechsel vonDELAYnachLIGHT, bei den anderen Zuständen hat er keine Auswirkung - Der Ausgang

led_oist auf'1', wenn die Zustandmaschine im ZustandLIGHTist - Der Ausgang

timer_enable_oist im ZustandDELAYauf'1', ansonsten'0' - Der Ausgang

timer_clear_oist im ZustandOFFauf'1', ansonsten'0'

Implementierung des Top Levels

5 Punkte

Zur Verfügung stehen die Komponenten counter, button_dectect und led_delay_fsm. Diese Komponenten werden genutzt, um im Top Level led_delay.vhd die gewünschte Funktionalität zu realisieren.

- Die Instanz der Komponente button_detect mit dem Namen

toggle_detect_componentist bereits erstelltbutton_iist mit dem Eingangbutton_toggle_iverbundendetect_oist mit dem (bereits definiertem) Signaltoggle_detectverbunden

- Erstelle eine Instanz der Komponente button_detect mit dem Namen

on_detect_componentanalog zutoggle_detect_componentbutton_iist mit dem Eingangbutton_on_iverbundendetect_oist mit dem (bereits definiertem) Signalon_detectverbunden

- Erstelle eine Instanz der Komponente led_delay_fsm mit dem Namen

led_delay_fsm_componenttoggle_iist mit dem Signaltoggle_detectverbundenon_iist mit dem Signalon_detectverbundentimeout_iist mit dem (bereits definiertem) Signaltimeoutverbundenled_oist mit dem Ausgangled_overbundentimer_enable_oist mit dem (bereits definiertem) Signaltimer_enableverbundentimer_clear_oist mit dem (bereits definiertem) Signaltimer_clearverbunden

- Erstelle eine Instanz der Komponente counter mit dem Namen

timeout_componentWIDTHin der generic map wird auf 28 gestellt (28 Bit)MAXIMUMwird aufCLK_TIMEOUT_DIVIDERgestellt (ist im generic Teil des Top Levels bereits definiert)enable_iist mit dem Signaltimer_enableverbundenreset_iist mit dem Signaltimer_clearverbundenvalue_oist nicht verbunden (open)overflow_oist mit dem Signaltimeoutverbunden

- Jede Komponente hat einen Takteingang

clk, welcher mit dem globalenclkverbunden wird

Erweiterung der Constraints Datei

2 Punkte

In der Datei led_delay.ucf ist nur das Signal clk definiert. Erweitere die Datei um folgende Zuordnungen

button_toggle_iwird durch den Taster BTN0 angesteuertbutton_on_iwird durch den Taster BTN1 angesteuertled_oist die LED LD0

Test am Board

1 Punkt

Synthetisiere das Projekt und teste das Ergebnis am Board

Würfel

Vorbereitung

- Projekt dice/dice.xise öffnen

Aufgabenstellung

Mittels sieben LEDs wird ein Würfel dargestellt. Eine Taste startet durch das Drücken einen Zufallsgenerator und beim Loslassen wird das Ergebnis angezeigt. Dieser Zufallsgenerator ist ein Zähler, der mit 50Mhz die 6 möglichen Zustände durchwechselt.

Decoder testen

5 Punkte

Der Decoder wandelt den Eingang value_i (3 Bit) in die entsprechende 7 LEDs Darstellung leds_o (7 Bit) um. Dabei wird folgende Kodierung verwendet:

| LED6 | LED5 | LED4 | LED3 | LED2 | LED1 | LED0 |

|---|---|---|---|---|---|---|

| Aus | Aus | Aus | Ein | Aus | Aus | Aus |

| Aus | Aus | Ein | Aus | Ein | Aus | Aus |

| Aus | Ein | Aus | Ein | Aus | Ein | Aus |

| Ein | Aus | Ein | Aus | Ein | Aus | Ein |

| Ein | Ein | Aus | Ein | Aus | Ein | Ein |

| Ein | Ein | Ein | Aus | Ein | Ein | Ein |

- Die erste Zeile entspricht der Darstellung bei

value_igleich"000" - Ein wird mittels

'1'kodiert, Aus mittels'0' - Bei nicht definierten Zustände sollen alle LEDs aus sein

Die Komponente ist in vier Ausführungen (Architectures) bereits in der Datei decoder.vhd beschrieben. Die Architectures lauten behave1, behave2, behave3 und behave4.

Erstelle in der Datei decoder_tb.vhd eine Testbench, die herausfindet, welche der vier Ausführungen funktioniert (es ist genau eine).

Komponente shuffle

5 Punkte

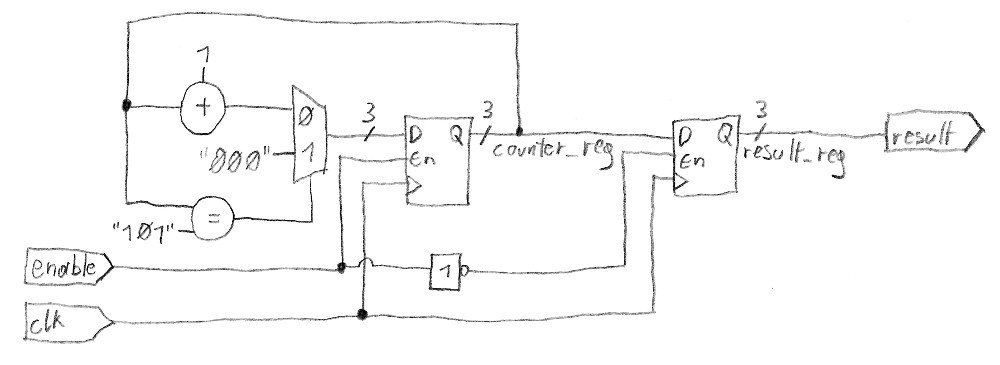

Erstelle die Komponente shuffle durch Bearbeitung der Datei shuffle.vhd nach folgender Skizze:

- Wenn

enable_iauf'1'ist, soll der interne Zählercounter_regbei einer steigenden Taktflanke hinaufzählen - Der interne Zähler soll von 0 bis 5 zählen

- Das Register

result_regübernimmt bei einer steigenden Taktflanke den Wert voncounter_reg, wennenable_igleich'0'ist

Implementierung des Top Levels

5 Punkte

Zur Verfügung stehen die Komponenten shuffle, decoder. Diese Komponenten werden genutzt, um im Top Level dice.vhd die gewünschte Funktionalität zu realisieren.

Test am Board

1 Punkt

Synthetisiere das Projekt und teste das Ergebnis am Board